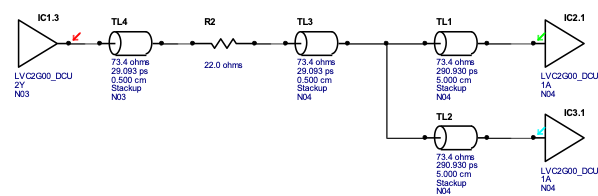

今回は1対多のBUS信号など多分岐している信号について、波形がどのように変化するかシミュレーションで確認してみます。

レシーバが多くぶら下がっている信号は波形が乱れます。

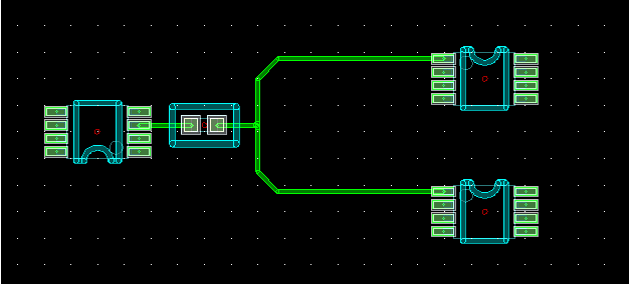

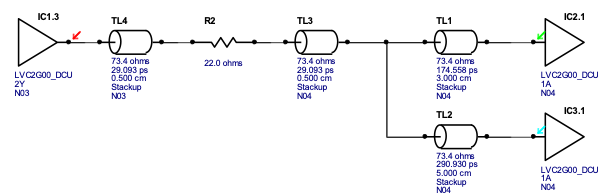

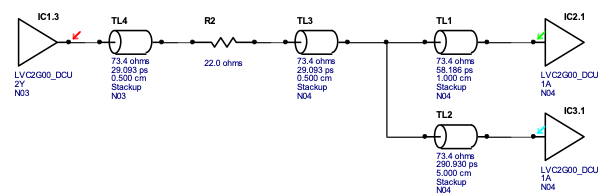

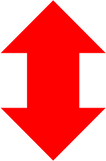

イメージ図の様にドライバ側にあるダンピング抵抗近くから分岐して配線するような状況で

メモリ関係の配線などにも見られます。

負荷は同じもので確認しています。

イメージ図

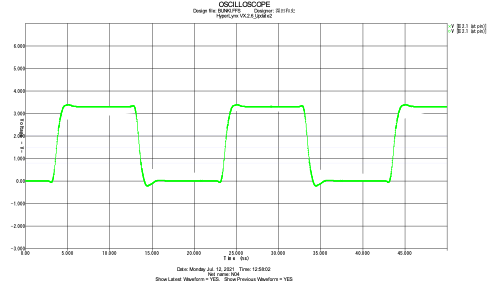

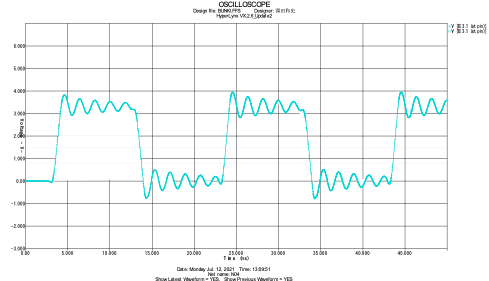

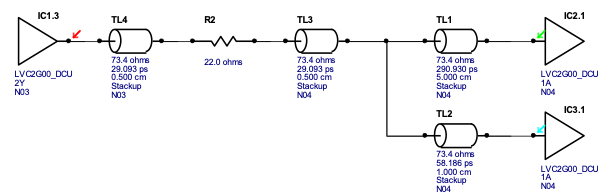

●ダンピング抵抗近くから長さを揃えて分岐した場合、同じ波形で乱れもありません。

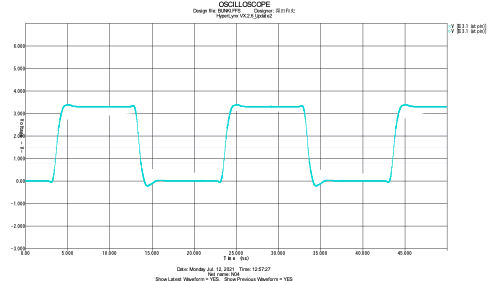

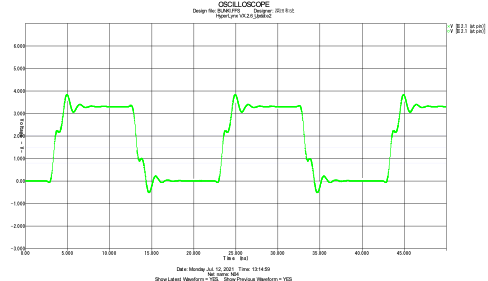

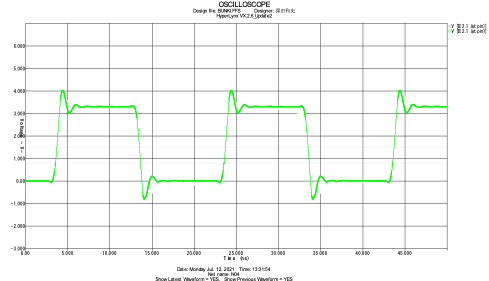

●IC2側の配線を短くした場合、どちらもリンギングが発生しました。

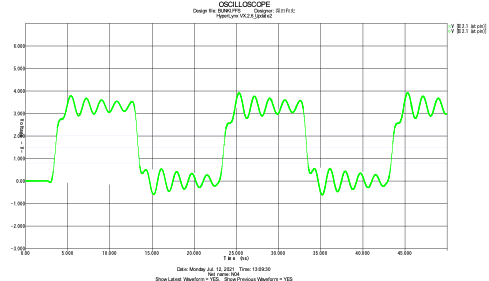

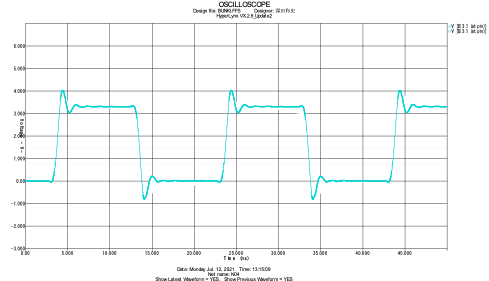

●IC2側の配線をかなり短くした場合

短くしたIC2側の波形のエッジに段付きの兆候が見られました。

短くしたほうの波形が悪くなっているようです。

●IC1側の配線をかなり短くした場合

短くしたIC1側の波形のエッジに段付きの兆候が見られました。

配線の長さを入れ替えても短く配線したほうの波形が悪くなりました。

2分岐での波形を確認してみましたが、分岐後の配線長が同じであれば波形の乱れはありませんでした。

配線パターンの長い方が波形が悪くなるような気もしますが、分岐後の長さは短い方が波形が悪くなっていることも確認できました。

分岐後の等長配線は基板設計の難易度が上がってしまいますのでシミュレーションをして進め方を決めておくことがおすすめです。