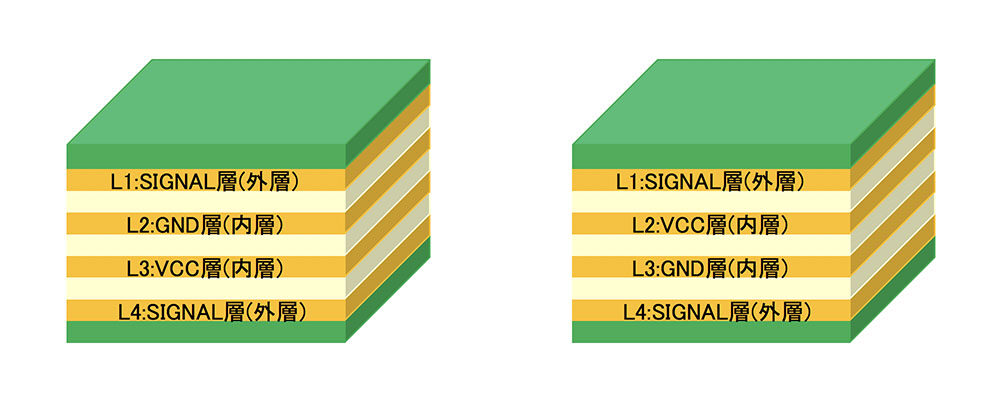

基板の層数が4層以上の多層板の場合、一般的な基板の層構成は

基板の層数が4層以上の多層板の場合、一般的な基板の層構成は

L1層、L4層がSIGNAL層(信号配線層)、L2層またはL3層がGND層、VCC層という層構成となります。

多層基板になると、基板上には層間接続用の信号ビアや電源、GNDビアなどが多数配置されると思いますが、

今回は、内層での電源パターンを配線する場合の配線方法で気を付けなければいけない事をご紹介します。

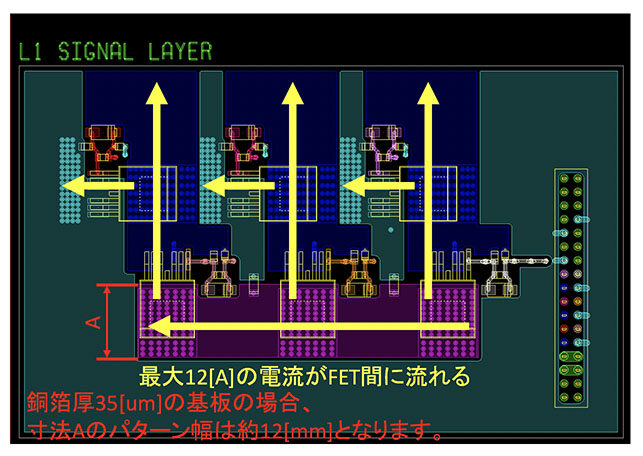

今回の事例はFETを使用したパワー系の回路構成です。

FETのドレイン(桃色)→ソース(青色)→GND間には最大12[A]の電流が流れるとします。

銅箔厚35[um]の基板でパターン幅1[mm]に流せる電流値は一般的に1[A]と言われていますので、

12[A]の電流を許容する為には、パターン幅を12[mm]確保する必要があります。

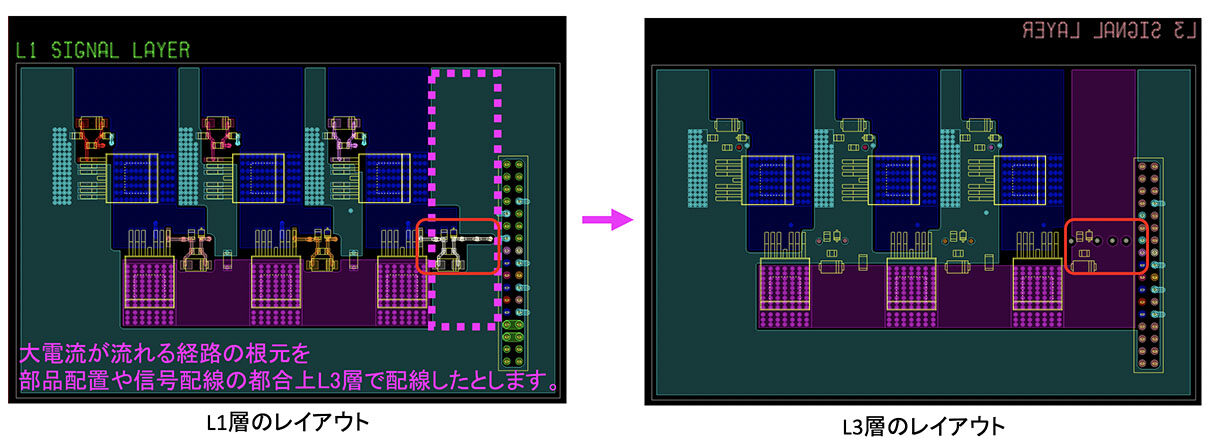

今回の基板レイアウトでは部品配置や信号配線の都合上、大電流が流れる経路の根元をL3層で配線したとします。

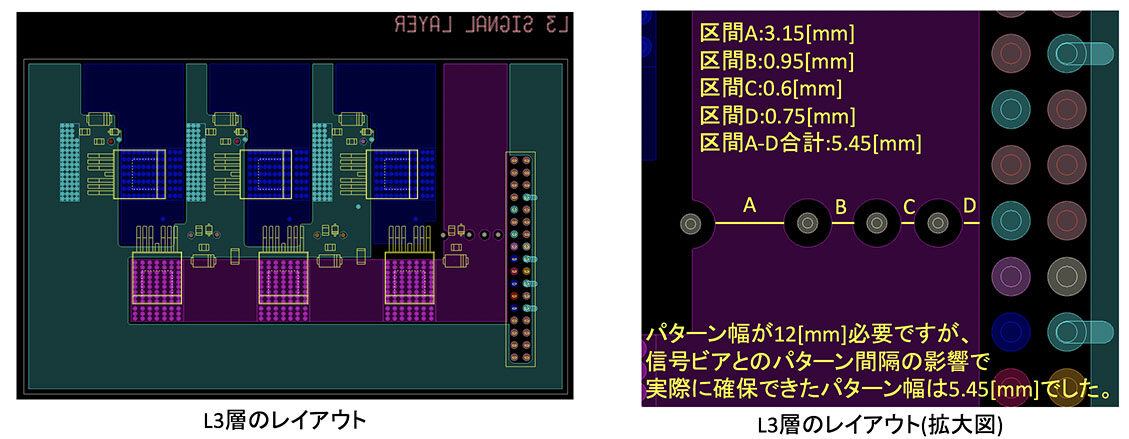

赤枠の部分にはFETのゲート端子の周辺部品の配線ビアが複数配置されているので、L3層の大電流が流れる桃色のパターンはビアとパターン間隔を取る為にパターン幅が削られてしまいます。

大電流経路で信号ビアとパターン間隔を取る為に削れてしまった部分のパターン幅を確認します。

ビアとビアの間に残ったパターン(区間A-D)のパターン幅を測定すると区間A-Dのパターン幅の合計は5.45[mm]となります。

大電流部は12[A]流れる経路なので必要パターン幅は12[mm]ですが、実際に確保できたパターン幅は5.45[mm]とパターン幅はかなり不足している状況です。

一般的に銅箔厚35[um]の基板でパターン幅12[mm]の配線へ12[A]の電流を流した場合、パターンの温度上昇は約10[℃]上昇となりますが、

今回の事例のようにパターン幅5.45[mm]の配線へ12[A]の電流を流した場合、パターンの温度上昇は約60[℃]上昇という結果となり、

必要パターン幅を確保した場合と温度上昇がかなり増える結果となりました。

プリント基板上で電流が多く流れるラインを設計するにあたっては、発熱をできるだけ低減させる為に、大電流が流れる配線のパターン幅を可能な限り確保することが求められます。

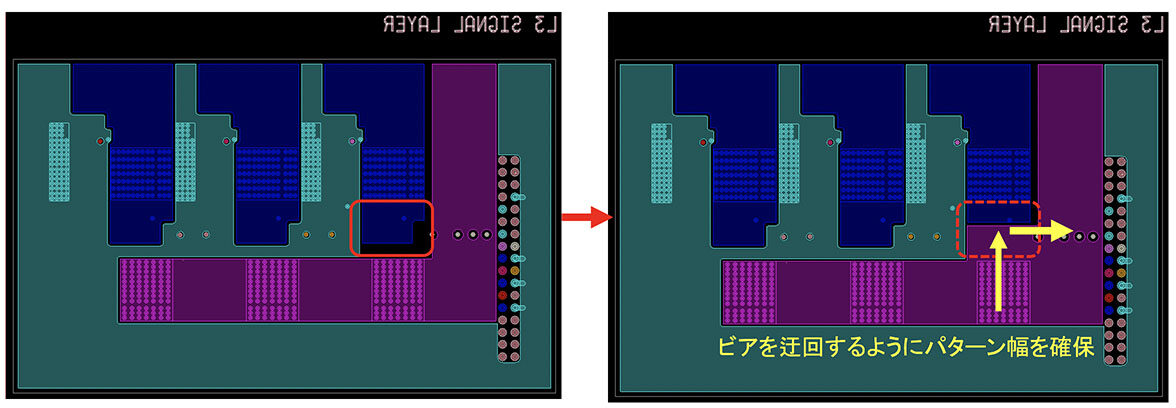

今回の事例の対策としては、赤枠部のパターンを削除して桃色のパターン幅を増やす対策や、L3層とL4層など他の層を併用してパターン幅を合計12[mm]となるようにパターンを引くなどして、必要パターン幅を確保すると良いと思います。

また、予め、パターン幅12[mm]の配線を形成してその領域にはビアを設置しないようにして頂き、基板レイアウトができると一番良いと思います。